一.前言

进入2019年,随着5G商用的坚实推进,传递到数据中心和服务器的更高运算带宽的压力也越来越大。由此随着PCIE4.0规范的全面定稿,业界主要玩家从芯片供应商,到服务器系统研发生产厂家及中间部件厂家均全面开始启动。

基于此背景,本文将主要就PCIE4.0的测试项目及方法和方案作一简单说明。

先我们要明确的是近年来针对PCIE3.0和4.0测试通常分两大场景,Base即针对芯片测试和CEM(Card Electrical Mechanical)测试即俗称的金手指插槽接口信号测试。

通常Base测试是芯片供应商不可回避的环节,而CEM测试通常是以服务器及其周边设备为主的系统生产商的主要战场,相关产品包括以PC主板,服务器为代表的System Board;以及各种插卡,如独立显卡,高速网卡与通讯接口卡,加密卡等等为代表的Add-in Card;另外还有其它基于PCIE物理层规范进行信号传输的SSD等设备,通常遵循M.2或U.2接口,也转化遵循CEM规范进行测试。

以下主要针对CEM规范场景就测试方法及方案做一个简单的说明和探讨。

二.发送端测试说明和方案

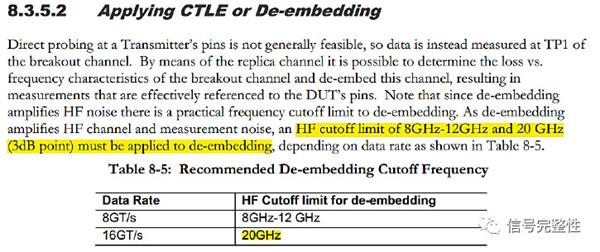

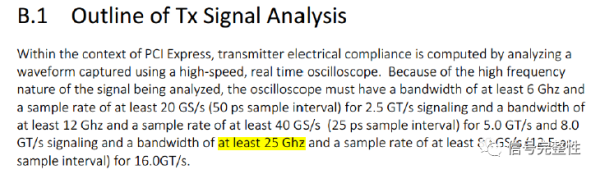

发送端测试主要设备是实时示波器。要工作是确定需要测量的信号频率范围,选择恰当的仪器带宽和型号。根据PCIE4.0 Base规范:

图1 PCIE4.0 Base规范对测试带宽需求的说明

针对PCIE4.0 16Gbps依据de-embedding Replica Channel的需要推荐的带宽范围在20GHz。

另外Base Spec 中也规定,由于Rx 测试所使用的BERT 输出上升沿要14ps~19ps(20%~80%),要求校准使用示波器带宽至少达到25GHz,同样,这也是对Tx 测试的小带宽要求。

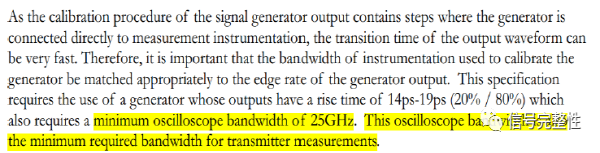

针对CEM 场景测试,根据PCI-Sig 相关文档和规范如下图:

图2 CEM Add-in Card和System测试方法描述 从以上两张图片可以看到具体在PHY Test Spec规范中明确推荐25GHz带宽示波器。

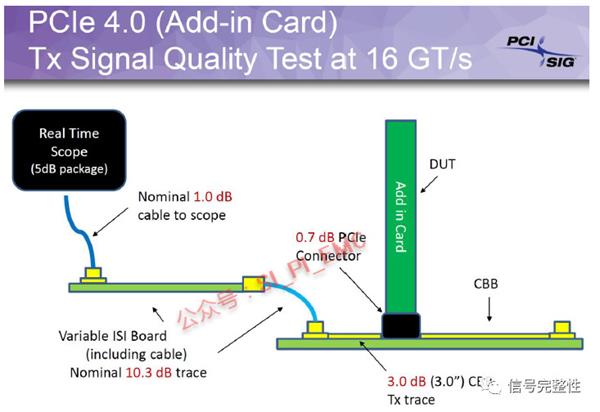

Keysight DSAV254A,DSAZ254A及UXR0254A三款示波器均可以支持.其中UXR系列采用10bit ADC相对前两款有更高ADC位数及本底噪声,会带来更高测量精度及更多的裕量。测试连接框图如下:

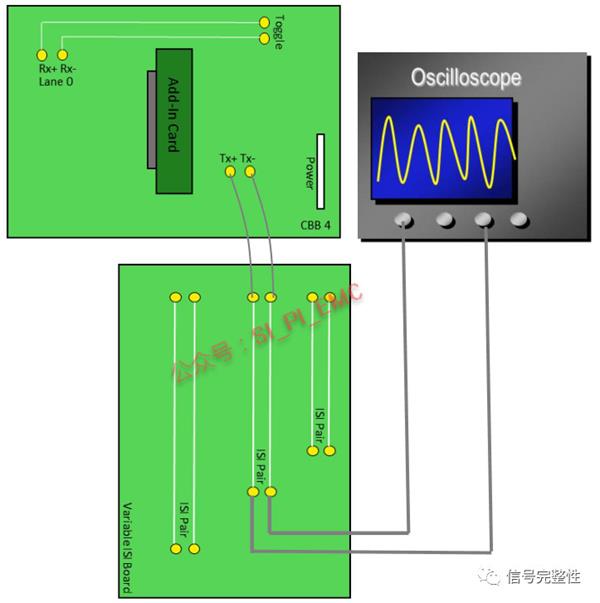

图3 Add-in Card TX测试连接示意图

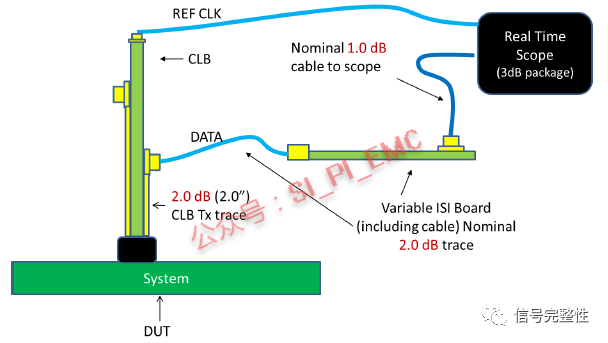

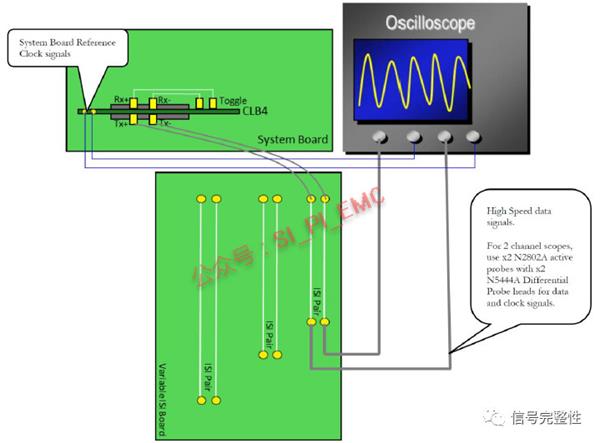

下面这张图为针对Sys Board的Dual Port测试的组网图:

图4 System Board TX测试连接示意图

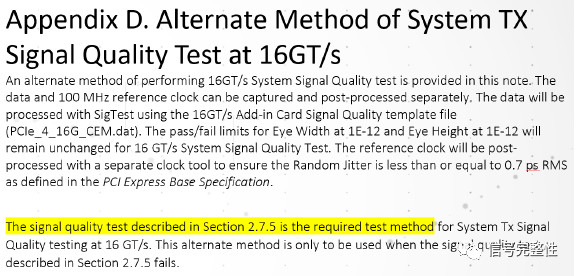

在PCIE4.0 Phy Test Spec里,关于System采用Dual Port测试Appendix D有如下描述:

图5 PCIE4.0 Test Spec Appendix D替代方法说明

注意上面黄色高亮文字,明确说明必须采用2.7.5描述方法。只有在采用2.7.5方法测试失败后,才可以采用替代的数据和时钟分开采集再对时钟进行后处理的方法。

因此必须要补充说明的是:

a.双端口测试始终是PCIe 4.0 System Board测试的必须方法。

b.添加了附录D仅作为应急。如果启用了大SSC,Sigtest软件处理会显示问题。开发人员用新方法近已经解决了Sigtest 在处理SSC时的问题。

c.在近的WorkShop #110上测试的所有系统板均使用双端口方法进行了测试。

d.双端口方法同时使用时钟和数据测试,基于End Device角度很好地诠释了根组件的信号质量。

e.系统板供应商可以针对参考时钟做抖动平衡或折中,以获得更好的信号抖动,并且仍然符合规范。

PCIE4.0测试夹具如下图:

图6 PCIE4.0测试夹具

PCIE4.0的夹具都是在协会官方网站购买,链接如下:

http://pcisig.com/specifications/order-form

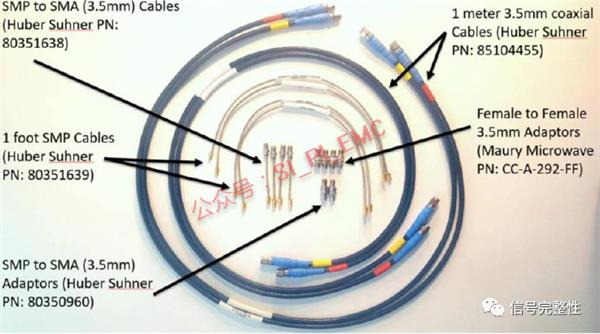

协会夹具套件除了上述的夹具板外,也包含了下图中的4根银色1英尺SMP-SMP cable及4根银色SMA-SMP短电缆,其余电缆和转接头需要自行额外购买。

图7 测试用同轴电缆和连接器等附件

以及为了端接CBB 和CLB 上的非在测链路,需要30 个SMP,50 欧姆端接器,Male,推荐型号Fairview Microwave PN/ST1847.

另外针对Add-in Card 测试,需要一台 带24 针连接器的ATX 电源用于供电。

为了保护客户投资,针对已有DSAV254A 设备情况下,由于其支持2 通道25GHz 示波器,而对Root Complex 类DUT 在进行System Board 测试时需要Dual Port 方法进行测试。即同时接入差分时钟和数据,如果采用全电缆连接则需要2 个通道分别接入时钟信号CLK+和CLK-,2 个通道分别接入Data+和Data-,因此就需要4 个通道25GHz 带宽示波器。因此PCI-Sig 组织允许采用2根高带宽差分探头配合SMA 探头前端,分别接入差分数据和时钟进行测试。推荐的探头和SMA探头前端是N2802A 以上和N5444A SMA 前端。

图8 差分探头和N5444A SMA 探头前端

数据分析软件,针对PCIE4.0,推荐PCI-Sig Sigtest 4.0.48 以上,下载链接:

http://www.intel.com/high-speed-io.

针对低速信号,2.5G/5G/8G,推荐使用Sigtest 3.2.0.3,并遵循PCIE3.0测试流程。

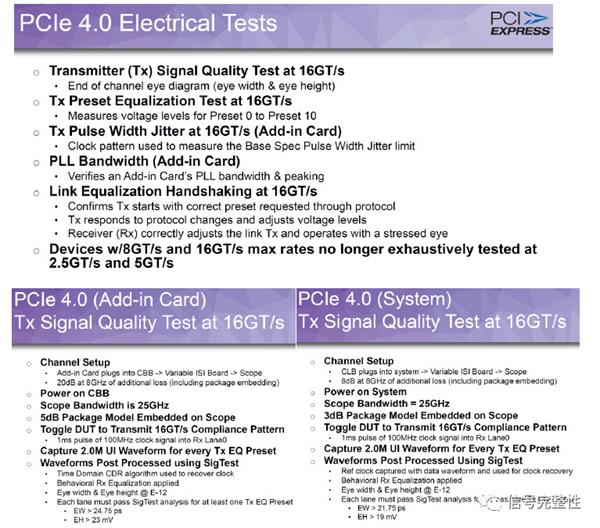

针对System Board和Add-in Card主要有如下测试项目:

[PHY 2.1] Add-in Card Transmitter Signal Quality Test for 16GT/s

[PHY 2.2]Add-in Card Transmitter Pulse Width Jitter Test at 16 GT/s [PHY 2.3] Add-in Card Transmitter Preset Test for 16GT/s

[PHY 2.7] System Board Transmitter Signal Quality Test for 16GT/s

[PHY 2.8] System Board Transmitter Preset Test for 16GT/s

下面我们就这几个项目做一简单的说明。

[PHY 2.2]项目主要是针对AIC进行,按压切换按钮,第27个设置,0/8/16/24链路会输出Jitter Measurement Pattern,设定示波器捕获2M UI存储波形后用Sigtest上的PCIE_4_0_CARD\PCIe_4_16GB_Tx_PWJ.dat模板进行测试。

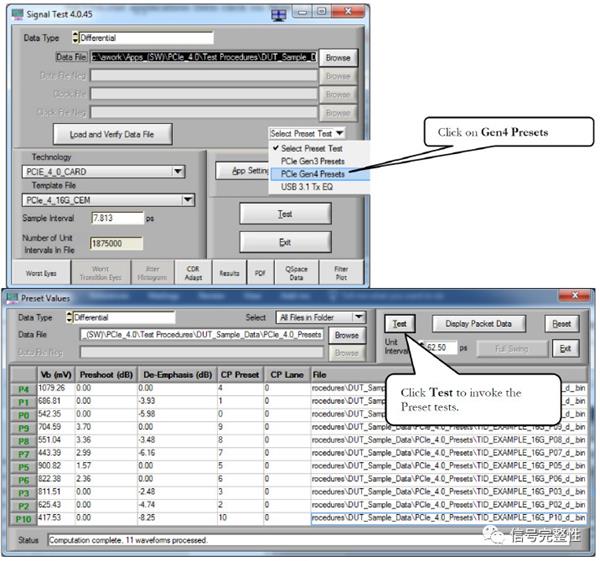

[PHY 2.3]和[PHY 2.8]是分别针对 Add-in Card和System Board的16GT/s的 Transmitter Preset测试。沿袭自PCIE3.0 8GT/s,在4.0标准上全部保留了P0-P10共11个Preset:

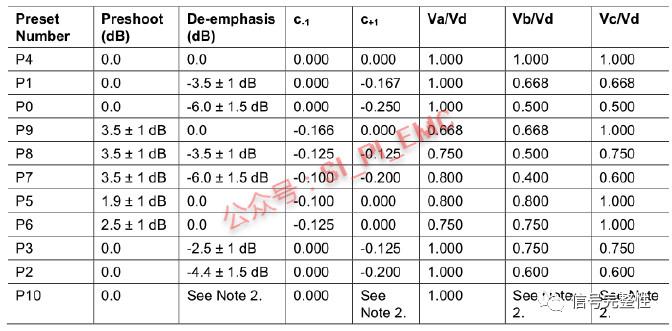

表1 PCIE4.0 Preset表

这个测试过程要确定被测设备是否为11个(P0-P10)预设中的每一个产生正确的TX发送器均衡。这些正确的均衡主要是为了在发送端针对码型跳变时预留足够的高频分量以应对传输链路的损耗。

[PHY 2.1]和[PHY 2.7]是分别针对AIC和SYS_Board的信号质量测试。按CBB4/CLB4夹具上的一致性模式切换按钮,直到到达Gen4 P0。建议先复位被测系统并计算按钮按下次数,直到您循环通过2.5G,5G和8GT / s一致性信号。PCI-SIG的一致性测试程序要求其中一个预设(P0-P10)

通过PCIe 4.0 CEM信号质量测试。可以选择任何预设; 然而,在初步测试中发现Preset P5通常会给出迄今为止测试的大多数设备的通过结果。也可以测试其他预设,但必须至少有一个预设通过测试才能符合信号质量的一致性要求。

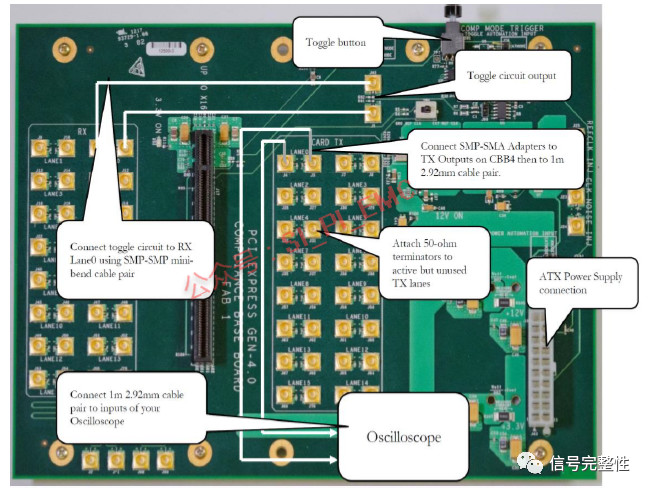

图9 用于Add-in Card发送端预设测试的CBB夹具示意

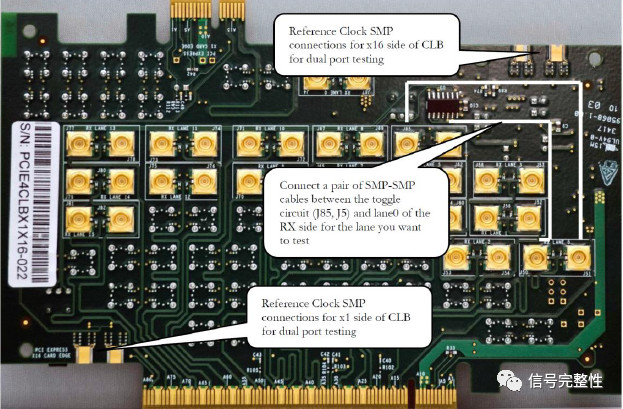

图10 用于System Board 发送端预设测试的CLB X1X16 夹具示意

特别提醒注意的是在进行TX 测试时,如果采用手动Preset 切换,需要在CBB/CLB 夹具上连接Toggle Circuits 和RX Lane0。CBB 上的连接只有一种情况,而在采用CLB 夹具时会因为X1/X16和X4/X8 的不同以及CEM 插槽的差异而不同,比如针对X16 插槽测试就采用两根SMP-SMP 电缆连接J85/J5 Toggle Circuits SMP 接口到RX Lane0 的J50/J51,如上图所示。

在捕获所有预设波形后并保存在一个相同目录下,就可以采用Sigtest 进行测试。

图11 Sigtest测试设置和结果

[PHY 2.1] 和[PHY 2.7]是分别针对Add-in Card和System Board的发送端 16GT/s Signal Quality 测试。这两个测试项目验证被测设备的信号是否符合眼图和抖动等其他要求。未测试的链路应使用50欧姆SMP终端器进行端接。

下图分别是针对Add-in Card和System Board测试连接示意图:

图12 Add-in Card信号质量测试示意图

注意Add-in Card测试只要两根电缆接入数据+和-到示波器的两条输入通道。而System Board则必须采用Dual Port测试,需要同时接入时钟和数据信号进行测试,当前PCI-Sig组织推荐采用四通道25GHz带宽示波器分别接入CLK+,CLK-和DATA+和DATA-四根信号。基于对过往投资的保护,也认可了采用高带宽差分探头加SMA探头前端直接接入CLK和DATA差分对的方法。

图13 System Board信号质量测试示意图

另外相对于以往PCIE3.0的测试可以看到在进行眼图和抖动等信号质量测试时,引入了ISI夹具,以满足整个测试链路28dB的损耗。如果采用前面列出的推荐的电缆和连接器附件,在Add-in Card测试时缺省推荐采用Pair 16,在System Board测试时缺省推荐采用Pair 0。在实际工作中,由于ISI夹具为硬件实物,可能存在差异性,遇到采用上述两个推荐ISI链路时测试无法通过就需要采用网络分析仪评估被测DUT上链路损耗以及ISI夹具上不同线对的损耗,以决定采用一个优链路。

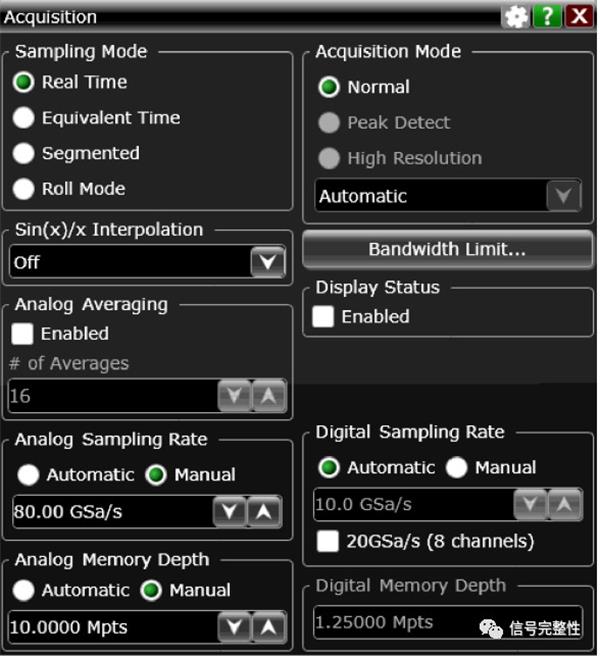

其它与PCIE3.0有显著不同的是明确说明需要捕获2M UI进行数据分析。针对PCIE4.0 16GT/s,如果采用V/Z系列示波器,设定高采样率80GSa/s,需要的记录深度:

存储深度=捕获时长*采样率=(2M*1/16G)*80G=10M

如果采用UXR系列25GHz示波器,设定高采样率128GSa/s,需要的记录深度:

存储深度=捕获时长*采样率=(2M*1/16G)*128G=16M

另外Sigtest处理的是示波器捕获的原始波形,需要将示波器的内插(interpolation)关闭(设置为off),以上两种设置均可在Keysight示波器的Setup→Acquisition页面下进行设置:

图14 V/Z/UXR系列示波器存储深度设置示意

在完成一些基本的示波器设置后,我们就可以看到屏幕上的原始波形。

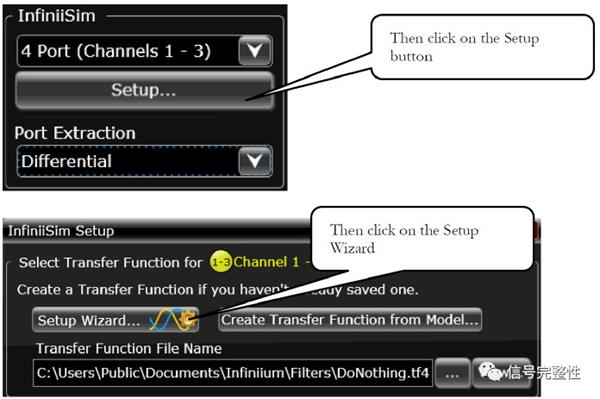

由于采用夹具接入信号,而夹具上是SMP连接器,不能完全等效于真实的芯片封装模型,因此PCI-Sig规范规定进行Add-in Card测试时,需要在示波器上模拟Root Complex 5dB封装模型,而在进行System Board测试时,需要在示波器上模拟End Point 3dB封装模型。

这一运算可以简单地在Keysight 实时示波器的软件里非常简单的设置完成。

在Setup菜单下,选择Channel设置,选择右下角InsiniiSim设置区域,如下图示。

图15 Infiniisim设置示意图

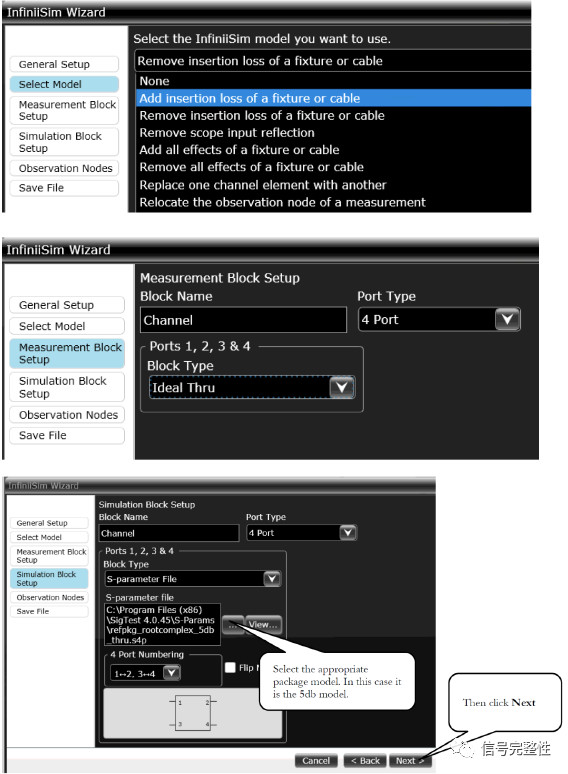

点击Setup按钮,进入InfiniiSim设置窗口,可以选择Setup Wizard,按照设置向导进行一步步设置。

图16 Infiniisim设置图

这里无论是进行Add-in Card还是System Board信号质量测试,都需要嵌入一个5dB或3dB封装模型。因此选择“Add Insertion Loss of a Fixture or cable”.按照下图操作顺序即可完成,封装模型的嵌入,模型参数在安装4.0.45版本以上Sigtest程序中,文件名是

针对 Add-in Card:refpkg_rootcomplex_5db_thru.s4p

或针对 System Board: refpkg_endpoint_3db_thru.s4p

图17 Infiniisim 设置图

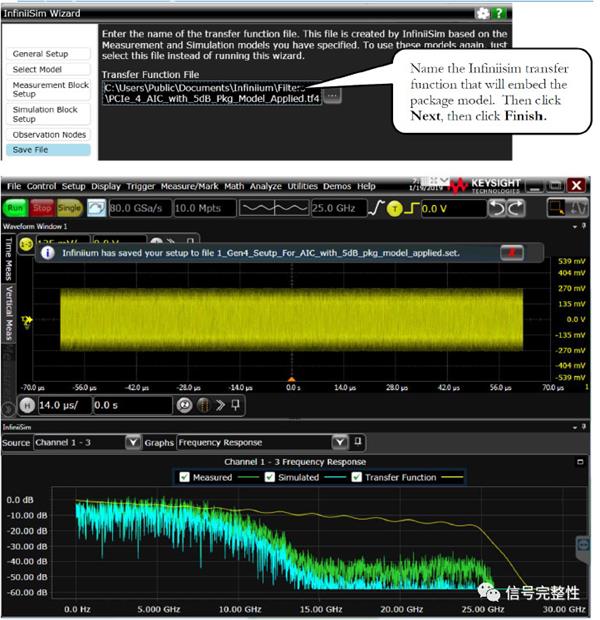

在完成模型嵌入后,示波器软件会生成一个传递函数并对捕获得到的波形进行一个数学运算得到嵌入处理后的结果:

图18 Infiniisim 处理完毕效果图

将捕获得到的波形存成bin 文件。

特别地在进行System Board 测试时,需要同时存储Data 和CLK 波形,应选择存储AllWaveforms,All Data。如下图示:

图19 波形存储示意图

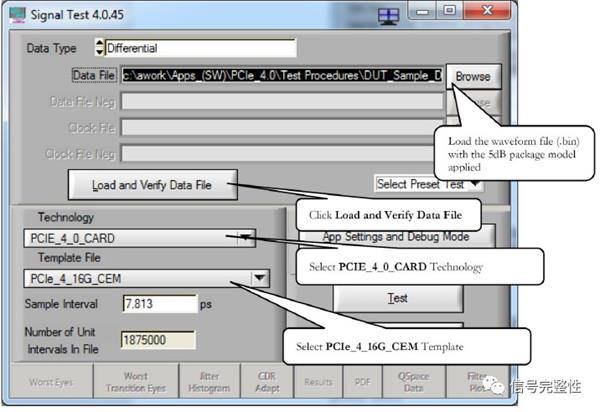

波形存储完毕后即可在Sigtest软件里进行测试:

图20 Sigtest设置界面

点击Test按钮,就可以得到如下测试结果和报告:

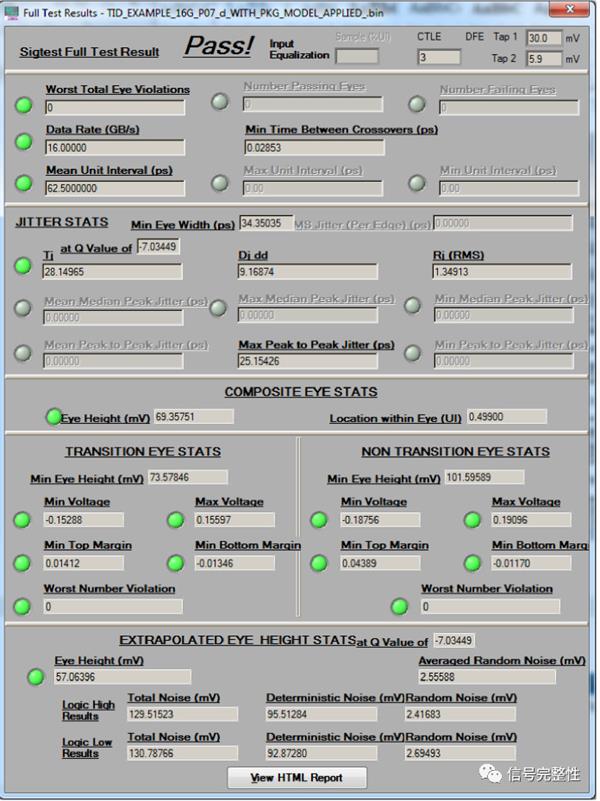

图21 Sigtest测试报告结果图

除了可以使用由Intel 提供的Sigtest 软件外,也可以采用Keysight N5393G PCIE 一致性测试软件进行信号分析并给出标准的一致性测试报告:

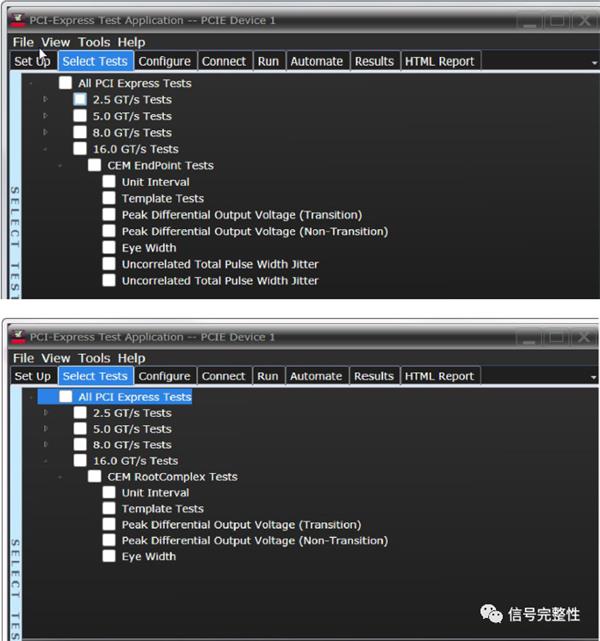

图22 PCIE 一致性测试软件界面