实时示波器面临的挑战

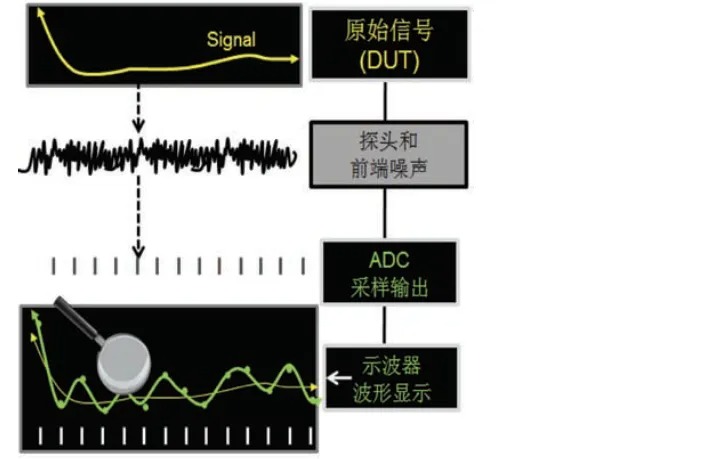

数字技术发展的同时也在推动着测试和测量技术的发展,因此主要工具实时示波器也需要不断地更新换代和创新发展。衡量数字实时示波器的指标有很多,往往使人分不清主次。早期,我们对示波器的关注更多的是在四个常规指标,如带宽,采样率,存储深度和触发的重要性。 现如今高速信号测量的挑战越来越大,不同品牌指标的示波器测量结果可能会存在比较大的误差。对于高速信号的测量来说,除了通用常规指标外, 实际上重要的但却较为抽象的衡量标准是信号保真度(Signal Fidelity),简单地说,信号保真度就是示波器显示的波形和被测电路的实际波形的一致性。但是由于信号进入示波器后会经过内部各个环节,而每一个环节都有可能对原始信号产生影响,从而导致示波器显示出的波形和实际波形存在偏差,而这种偏差又是用户很难去进行验证的,因此对于现代的高速示波器来说,我们还需要更多地关注在带宽以及本底噪声、ADC 有效位数等体现信号保真度的指标上。

图 1. 影响高速信号保真度的关键指标

更高带宽的需求

示波器作为常用的测试分析工具,发展主要有两个趋势,其一是性能的提升。自 Keysight 从 20 世纪 80 年代推出世界一款数字示波器后,数字示波器技术开始不断发展,其带宽从早期上百兆发展到现如今上百 GHz 的频率,示波器在性能上获得了飞跃的发展。另一方面随着高速数字设计的挑战性越来越高,示波器不仅要具备基本的测量功能,同时还要求具有强大丰富的分析能力,能够帮助用户对高速信号进行调试和分析,解决高速电路设计上存在的缺陷。

现代电子设计面临越来越多的挑战,近几年来,计算机、移动设备和云计算等领域的发展驱动着更高数据吞吐量的需求,为了满足这种需求,诞生了很多新的技术标准,如 USB3.x(10Gbps)、 Thunderbolt3(20.625Gbps)、M-PHY4.0(11.6Gbps)、PCIe 4.0(16Gbps)、SAS(24Gbps)、Fibre Channel(32Gbps)、400G PAM4(112Gbps) 等;这些高速串行总线的速率非常快,这就要求在测试中数字示波器具备更高的带宽。我们以传统的 NRZ 编码的数字信号来说,目前快的信号速率可达 50Gbps,如果按照理论计算需要测量到 3 次谐波,则需要 75GHz 带宽 ;如需要测量到 5 次谐波,则需要 125GHz 以上的带宽示波器。随着信号速率的提升和边沿跳变时间越来越快,为了能够地捕获真实的快沿信号,这就对示波器的带宽提出了更高的要求。

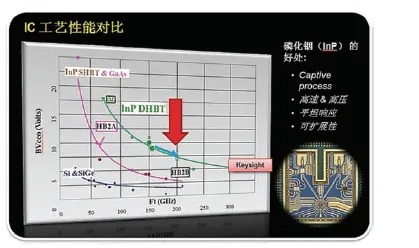

在 2010 年之前,示波器行业主要采用传统的锗化硅 (SiGe) 或者砷化镓 (GaAs) 材料。SiGe 材料相比 GaAs 虽然有更高的开关速度 ( 意味着可以带来相对略高的带宽 ),但是其耐击穿电压非常低,而 5V 电压是示波器行业在 50Ω 阻抗匹配下标准的容许高输入电压值,当采用 SiGe 材料的示波器带宽较高的时候,一般其容许大输入电压要远小于 5V。因此一些示波器厂商会推荐工程师在示波器通道外部额外增加不同的衰减器来扩大输入电压范围,但是额外增加的衰减需要在示波器内部再行放大或补偿,这必然导致仪器的本底噪声和抖动的恶化,从而在今天的超高速信号测试场景下导致裕量的无形损失也即带来更大的测试误差和测量结果的不一致性。

这种来自于产业界的持续发展对测试和测量行业也是非常巨大的挑战,必然要求在基础材料和半导体工艺上取得创新。磷化铟 (InP) 材料被用到测试测量行业就是因应这一挑战的大创新。

磷化铟 (InP) 材料具有电子漂移速度高、耐辐射性能好、导热好的优点。与 SiGe 半导体相比,它具有击穿电场、热导率、电子平均速度均高的特点。通过下面的材料性能对比可以看出,磷化铟半导体材料具有更高带宽的优势。这意味着用磷化铟 (InP) 材料制作的器件能够放大更高的频率或者更短波长的信号。利用磷化铟 (InP) 材料制成的放大器可以工作在 300GHz 以上的极高频率上,并且具有非常低的噪声,受外界影响较小,稳定性高,是一种更为先进的半导体材料。

图 2. IC 工艺性能对比

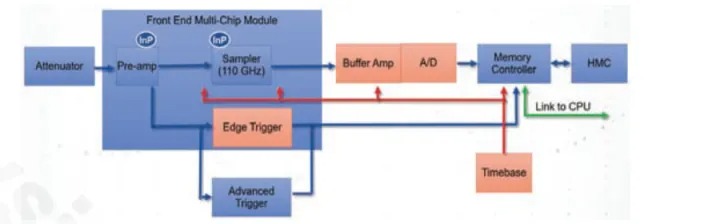

基于磷化铟 (InP) 的半导体材料技术,Keysight 推出了业内高带宽的 Infiniium UXR 系列实时示波器,其模拟带宽高达110GHz。相对于其他厂家 ATI (Asynchronous Timing Interleave) 或者 DBI (Digital Bandwidth Interleave) 采用先分频和分路采样后再合成的技术来说,Infiniium UXR 实时示波器则采用全带宽 110 GHz 的前端衰减放大器以及 110 GHz 的采保电路,实现了对输入模拟信号直接进行采样,从而摈弃了模拟信号经过重复的频域和时域转换以及数字信号再合成的处理技术,确保了佳的信号保真度。下图为 UXR 内部结构图。

事实上示波器作为宽频仪器,随着带宽越高则噪声会越大,其本底噪声通常表现为高斯白噪声分布。因此,对于高速信号的测量分析,我们不仅要关注示波器的带宽是否满足要求,还应该要关注其本底噪声性能。那么示波器的本底噪声对测试测量影响如何呢?

更低本底噪声的挑战

随着数字总线的速率越来越快和信号的幅度越来越低,在设计上其成本也会越来越高。比如在 PCIE4.0 的规范里, 眼高只有15mV 左右,未来到 PCIE5.0 则眼高可能只有 8-10mV。再比如下一代数据中心里高速信号互连的热门信号传输技术 PAM-4,由于采用 4 电平来进行信号传输,每个电平之间的幅度会非常小。从这些技术标准中都反应出在设计上对信噪比的要求开始越来越高。这也同时对测量仪器示波器的精度提出了更高的要求,要求更低的本底噪声以及更小的测量误差。

同时由于现在电子产业的竞争非常激烈,无论对芯片制造商还是系统设计商来说,都希望产品的测试结果有很大的裕量 (Margin)。对芯片厂商来说,希望有好的性能给下游系统设计商,让系统设计商知道该芯片有很大的设计空间,可以放心设计使用。而对于系统级的设计商来说,也希望可以知道系统测试的大裕量,然后可以确保测试 Pass 的前提下,进行 Cost down 缩减用料成本。为了可以使测试结果有更大的裕量,对测试仪器厂商来说,意味着仪器测试的保真度需要越来越高,测试误差越来越小,这是一个非常大的挑战。

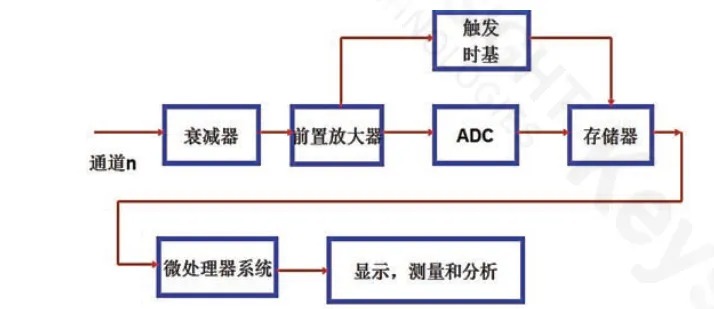

下面我们来看看示波器的本底噪声来自于哪里? 下图 1 是典型的数字示波器的架构 :

图 4. 示波器的典型结构图

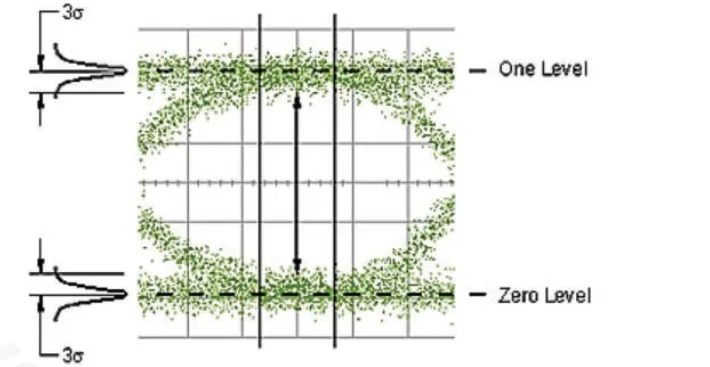

如果我们对高速串行信号进行眼图的测试,那么本底噪声会对其有什么样的影响呢?眼图测试的必测参数之一是眼高:

图 5. 本底噪声引入示意图

图 6. 眼图测试示意图

上图是一个典型的 NRZ 眼图测试各指标的示意图。其中眼高定义如下:

Vtopsigma 即为眼图顶部的噪声标准偏差或均方根值,Vbasesigma 为眼图底部的噪声标准偏差或均方根值。由此可见,眼高结果与波形噪声标准偏差有直接关系。而波形噪声标准偏差不仅仅与波形本身有关,如前文所述与示波器的本底噪声也是紧密相关的。

大多数示波器厂商会在示波器出厂之前对其进行噪声测量,并将测量结果列入到产品技术资料中。如果您没有找到相应信息,可以向厂商索要或是自行测试。示波器本底噪声测量非常简单,只需花上几分钟即可完成。首先,断开示波器前面板上的所有

输入连接,设置示波器为 50 Ohm 或者 1MOhm 输入路径。其次,设置存储器深度,比如 1 M 点,把采样率设为高值,以得到示波器全带宽。您也可以打开示波器的无限余辉显示,以查看测得波形的粗细。波形越粗,示波器的本底噪声越大。波形粗细可以直观反映示波器在该特定设置下的噪声大概范围,准确测量应通过 Vrms 交流测量来量化分析噪声情况。另外值得注意的是,如果需要对示波器的底噪声做验证或者对比,需要注意带宽、采样率、存储深度以及其他指标都需要保证在相同的环境下。

也有一些工程师了解示波器的噪声指标一般在 uV 或者 mV 级别范围,认为数值非常的低可以忽略不计。这样的想法是不正确的,由于示波器在底噪声测量时,通道都是断开的没有接入任何的外部信号,其自身的噪声信号是非常小的幅度。而在实际测量中,示波器会接入各种幅度的信号,比如 1.2V、2.5V、3.3V 信号等,如果外接探头的时候接入被测信号的幅度甚至会更高,这时候会受衰减比和量程设置等影响导致示波器底噪声会大大的恶化,会影响到测试结果的度。

另外在今天的高速数字差分信号测试和分析中,引入越来越多的去嵌处理 (De-embedding) 和均衡 (Equalization),这两种信号处理过程都会对示波器已经采集的信号进行放大,当然也会同步放大仪器的本底噪声,从而带来更大的测试误差,吞噬系统有限的裕量。

示波器的本底噪声不仅影响电压测量,也影响水平参数的测量精度。示波器的噪声越低,测量精度就会越高,测试结果的可信度也就越高。因此作为示波器前端部件性能的衡量指标的本底噪声数值就成为示波器产品手册上必须标注的一个指标。

示波器的本底噪声是影响信号测量精度的一个重要原因。而示波器的本底噪声性能除了跟示波器前端衰减放大器相关外,还有一个相关因素,那就是示波器的 ADC 模数转换器。ADC 的有效位数 ENOB(Effective Number of Bits) 越高,测量受到的误差影响就越小,测量结果的精准度也就越高。

对示波器 ADC 有效位数 (ENOB) 的追求更加凸显

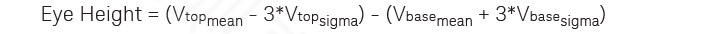

ADC 模数转换器是数字示波器里非常关键的部分,主要作用是将连续的模拟信号转换成离散的数字化采样点。提到 ADC 模数转换器,很多用户都会关注 ADC 的采样率,它代表每个采样点间的水平时间分辨率。足够的采样率也是保证示波器信号保真度的关键因数之一。但是并不一定意味着采样率越高,信号的保真度就越好。对于 ADC 来说,其位数也是非常重要的指标, ADC 的位数决定了采样过程中的量化等级或者垂直电压分辨率。大多数现代示波器通常 ADC 位数都是 8 比特,说明具有 256 个垂直量化等级。举例来说,如果一个 8 比特的示波器,其量程设定在 800mV 的时候,那么它的垂直量化等级就是 2 的 8 次方,也就是 256 个垂直量化等级,在当前量程下的垂直电压分辨率就等于 800 ÷ 28= 3.125mV。相同量程下,如果使用一个 10 比特的示波器,其大电压分辨率就等于 0.781mV。这也是为什么说 10 比特示波器会比传统 8 比特示波器的精度高 4 倍的原因。

图 7. 示波器 ADC 位数与测试误差

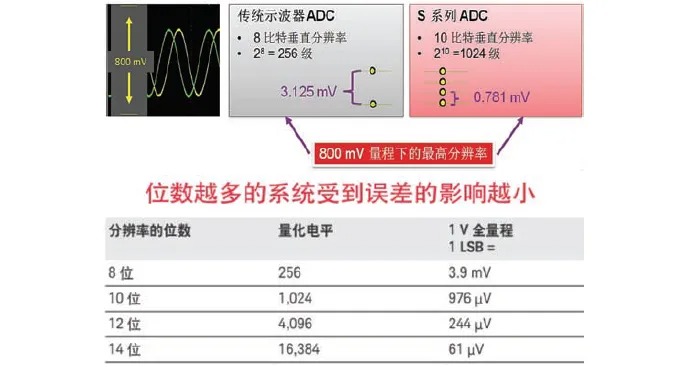

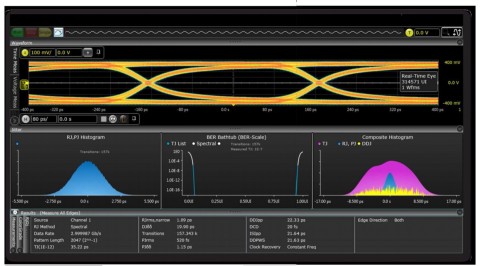

我们再来看下传统 8 比特示波器和 10 比特示波器的实测精度对比,下图是两款 4 GHz 带宽示波器测试同一个信号的眼图。左边是传统的 8 比特示波器 DSO9404A,右图是新一代的 10 比特 S 示波器 DSOS404A,两款示波器的带宽、采样率、垂直 /水平设置完全相同。可以看到,右图 Infiniium S 系列示波器由于采用 10 比特硬件的 ADC 以及低噪底等特性,更真实地在现了信号的眼图,眼图高度比左图高出 200 mV,提供了一个误差更小、精度更高的测量结果。由此可见,即便是同品牌同带宽的示波器产品,ADC 或者本底噪声的水平也是不同的。

图 8. 两款 4GHz 示波器眼图测试对比

ADC 的内部结构分很多种,像逐次逼近型,并行比较型 ( 闪烁型 ),分级型 ( 半闪烁型 ) 和流水线型等,每种都有优缺点,如FALSH ADC 线性误差高一些,流水线型有拼接误差等。对于ADC 性能的“好”与“坏”,我们不能仅仅靠采样率或者位数指标就进行判定。测试 ADC 的性能有很多的指标,比如 DNL、 INL、THD、SINAD、SFDR 等指标。IEEE 在 20 世纪后期定义了另一种方法,依靠 ENOB (Effective Number Of Bits) 有效位数技术指标来确定示波器 ADC 的“完好性”。有效位数 ENOB 指标的提出是因为当高速 ADC 进行数据采集时,由于噪声、谐波和杂散的影响,实际 ADC 的信噪失真比达不到其标称位数应达到的理想性能,比如很多通信中使用的 12bit ADC 在实际工作环境中有效位数只有 10bit 左右。事实上,有效位数 ENOB 总结了整个系统的分辨率并代表频率范围内的累积误差。

当我们选择示波器时,有效位数 ENOB 指标到底有多重要?它能有效判定示波器的测量精度吗?在数字示波器的架构中,和测量精度相关的电路包括示波器的前端电路和采用的ADC技术,前面提到的示波器的本底噪声主要来源就是前端电路。倘若示波器的前端电路的噪声过大,即便 ADC 具有较高的 ENOB,整个测量系统的性能也会明显下降。尽管某些示波器厂商会提供示波器 ADC 本身的 ENOB 指标,但光这一数值来说并没有太大意义。因为 ADC 仅为示波器系统的一部分,不能独立使用,要结合示波器前端电路,看整个示波器系统的 ENOB 指标才有意义。一般情况下,示波器厂商会对其使用的 ADC 芯片本身做内部评测,同时也会评测整个示波器系统的 ENOB。受示波器损耗的前端噪声、谐波失真和交叉失真等因素影响,整个示波器系统的 ENOB 会比独立 ADC 芯片的 ENOB 要低。另外,受高频宽带噪声的影响 ENOB 也会随频率的增加而降低。

有效位数 ENOB 值该如何进行测量呢?

ENOB 是用一个固定幅度正弦波信号进行频率扫描,在不同频率下对采集到的电压数据进行分析和评估。通常使用后期处理工具 ( 例如 MathWorks MATLAB) 对捕获所得的电压测量结果进行测评。用户可以在时域或频域中执行测量。使用时域方法测评信号时,把采集到的时域数据和一个据此拟合出的理想时域波形相减来计算 ENOB。计算相减的结果就是噪声,噪声可能来自示波器的前端,比如不同频率下相位的非线性和幅度变化,还有可能来自 ADC 拼接造成的交叉失真。在频域中测评相同的信号时,可以通过在整个宽带功率中减去与基带相关的功率来计算 ENOB。

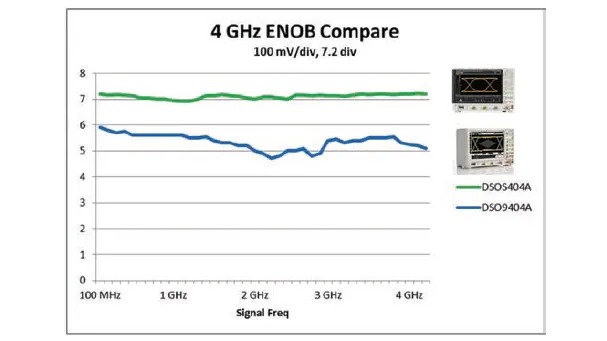

有效位数 ENOB 的值和频率有关,每款示波器都有自己的 ENOB曲线,值得注意的是,ENOB 曲线应该是针对示波器系统的,而不仅仅是其自身 ADC 芯片的。下图显示 Keysight 传统 8 比特9000 系列示波器和新一代 10 比特 S 系列示波器的实例 ENOB 图。该图显示的是整个示波器系统的 ENOB,而非示波器 ADC自身 的 ENOB。

图 9. S404A 示波器 ENOB

与本底噪声一样,ENOB 是测评示波器精度的重要指标之一。 ENOB 图应与本底噪声测量结果一起考虑。这是因为高速串行数据在特定频率会出现谐波,谐波通过示波器时几乎不会受到有效位降低的影响。在这种情况下,示波器本底噪声能够更好地反映测量精度。总之,ENOB 和本底噪声指标能够确保对示波器质量进行的测评,从而帮助工程师选择适当的仪器。

近年随着实时示波器带宽的持续推高,和信号电压幅度的持续降低,示波器的 ADC 位数也有持续提高的需要。实时示波器本身是宽频仪器,其带宽越高,在其整个频带范围内,噪声也会越大。因此如果高带宽实时示波器依然维持传统的 8bit ADC,那么在越高的频段上,由于其随机噪声的影响 ENOB 必然也会随之降低,例如一般 33GHz 带宽级别的实时示波器其 ENOB 在33GHz 频点只有 5bit 左右,有的厂家产品只有 4bit 左右甚至更低。在高速数字电路设计和测试技术发展的趋势里,产业界对高带宽、高 ADC 位数的实时示波器的需求已经开始凸显。

影响示波器的 ENOB 指标除了ADC 本身的位数外,还有示波器本身的插值误差即采样精度和示波器的本底噪声有关系,这是一个综合的评价指标。推荐阅读本文后列参考文献,《评估示波器的信号保真度》。

因应当前的技术发展和市场需求,Keysight 在 2018 年 7/12 重磅推出了新一代的 UXR 系列实时示波器,其带宽突破到业界高 110GHz,同时还提供了4 路通道,每路通道 256GSa/s 以及10 bit ADC 的业界高采样技术。在整个测量仪器行业内再次开创了先河成为行业标杆。

下图展示的是 Keysight 新一代 10bit ADC 的 UXR 系列高带宽示波器,具有更低本底噪声,与当前主流的 8bit ADC 的 Z 系列示波器测试同一个 PAM-4 信号的结果对比,很明显全新一代的10bit ADC UXR 示波器带来了更加优异的测量结果 :

图 10. 全新 10bit ADC UXR-63GHz 示波器和 8bit ADC Z-63GHz 示波器测试结果对比