通常说的信号完整性就是指信号无失真地进行传输。前面我们讨论很多信号完整性问题,包括时序、串扰、衰减、反射、电源完整性、EMC等等。

当前的电子产品PCB上或多或少都有一些是高速信号网络。在设计电路和PCB时就要多注意这些信号网络的信号完整性。

对于很多工程师来讲,信号完整性说起来是一句很简单的话,但是很多时候却要了硬件或者PCB设计工程师一条“老命”。本文主要针对PCB设计来讨论,看看在PCB设计时,有哪些点会导致信号完整性问题?

1、PCB材料选择

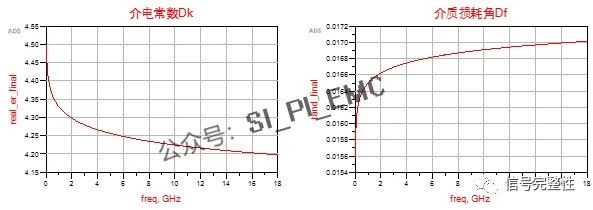

PCB使用什么样的PCB材料会直接影响到信号完整性。比如PCB材料的介电常数、介质损耗角、铜箔粗糙度、玻纤布等等参数都会影响信号的电气性能。如下是PCB材料的介电常数和介质损耗角随着频率变化的曲线。

PCB材料是基础,所以在设计PCB之前,要选择好合适的PCB材料。

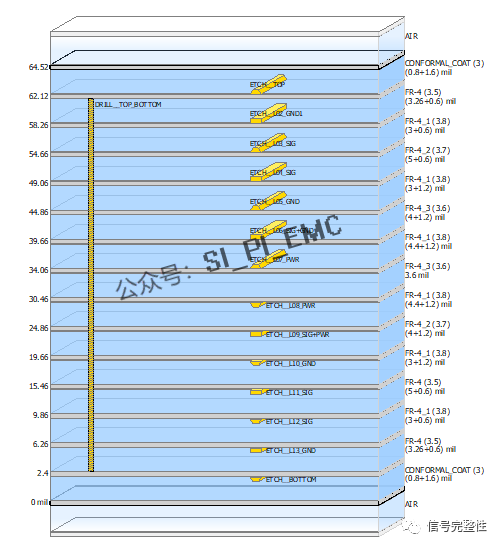

2、层叠设计

层叠设计是PCB设计中很重要的一步。如果层叠设计不合理,会直接导致设计存在天然的信号完整性问题。

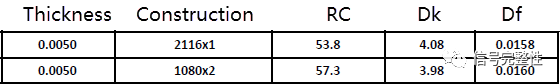

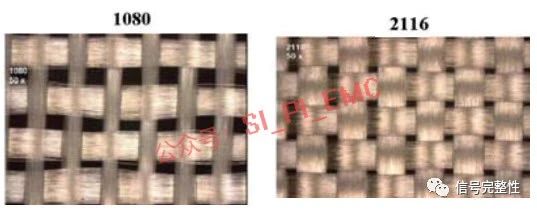

比如在设计层叠时,我们通常都是按照厚度选择,而对于相同的材料,也有很多种PP或者Core,那他们的性能并不是相同的,比如电气参数Dk/Df、玻纤规格等。如下是某材料的两种芯板:

虽然它们的厚度是一样的,但它们分别是由1张2116的PP组成和2张1080的PP组成。其Dk和Df并不相同。这样如果在设计层叠结构的随意使用,就会导致信号完整性的问题。同时,1080和2116的玻纤也不一样。

对于高速信号,还要注意玻纤效应的影响。关于玻纤效应,我们在前面的内容中也做过相关的介绍。

3、传输线的线宽

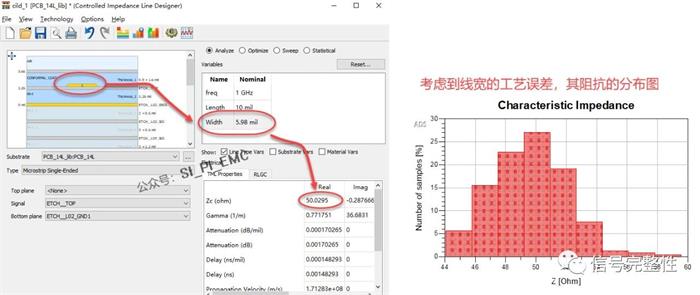

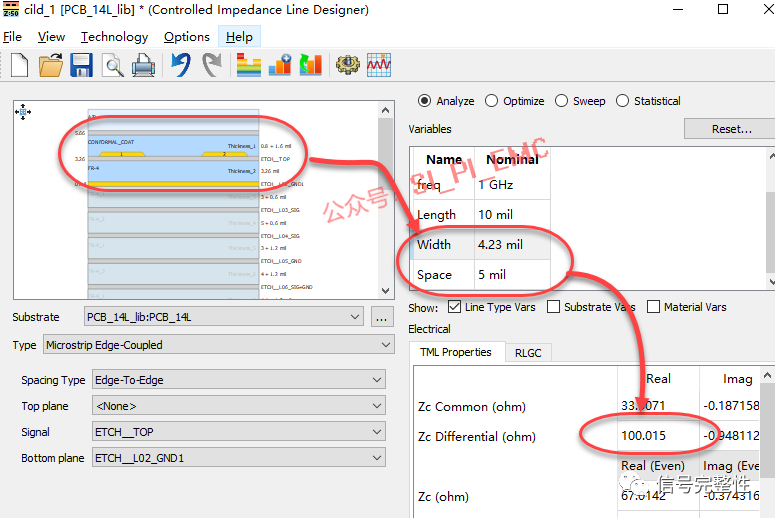

传输线的线宽是由阻抗决定的,根据总线或者芯片平台的要求,确定好传输线的阻抗;再根据阻抗,在ADS CILD中计算传输线的线宽。

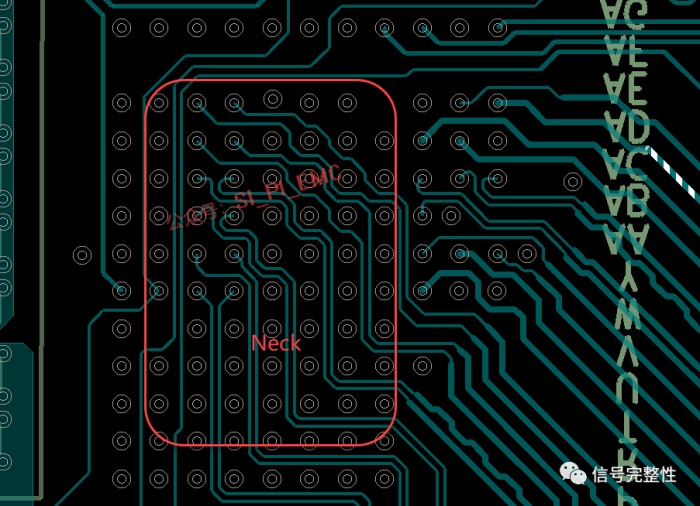

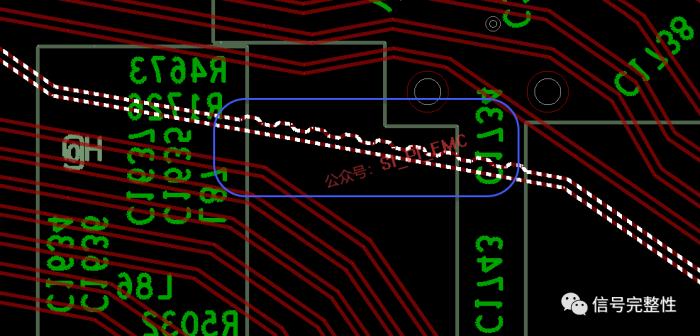

在设计PCB中,工程师都希望传输线的线宽是一致的,这样设计效率是高的,但是这很难保证,因为很多芯片、连接器这类器件的pitch都可能会比较小,或者引脚的密度很高,就会导致在设计中会把线宽变小。如下图所示:

线宽变化之后就会影响到信号完整性。在设计中要尽量减少这种线宽的变化,或者尽量缩短这种变化线宽的长度,等等。

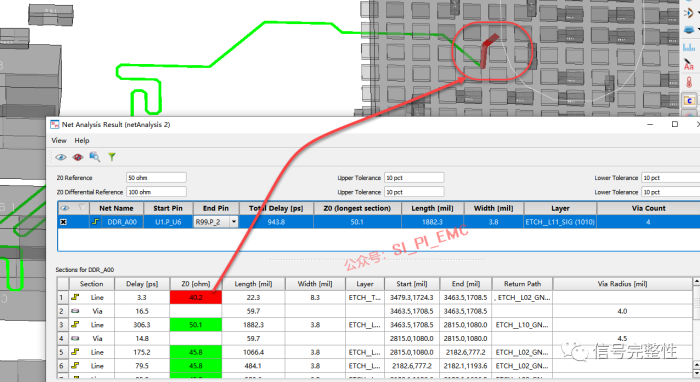

如果传输线太多,也可以考虑在ADS SIPro中使用RapidScan-Z快速扫描,查找到线宽变化,即阻抗不连续的点。

4、传输线之间的间距

在PCB设计中,传输线的间距有很多种类型,比如差分对内的间距,不同类型的传输线之间的间距等等。不同的间距要求不同,如果是差分对之间的间距,则不能太近(小),也不能太远(大),由阻抗和设计要求决定。

如果是不同类型传输线的间距,则希望间距尽量远一点,这样相互之间的串扰就会小,但是受限于空间和成本,这类间距也不能无限制的小。下面是随着间距变化,串扰的变化趋势。

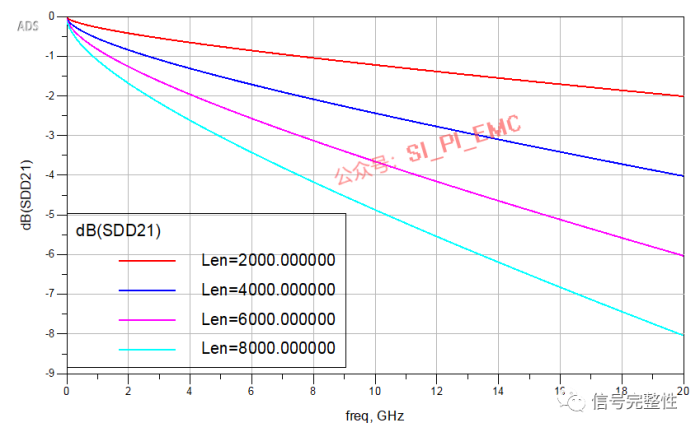

5、传输线的长度

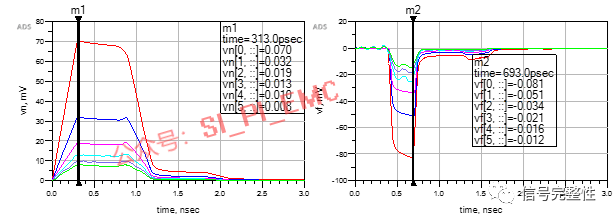

传输线的长度由于产品结构和实际设计决定。在没有特殊要求的情况下,都希望传输线设计的短一点。因为传输线越长,信号的衰减越大,能量损失越大。

如果传输线的长度确实很长,而又不能缩短,这种情况下可以考虑换低损耗的板材或者在链路上使用repeater。

6、传输线等长

等长这个概念其实是工程师“偷(聪)懒(明)”想出来的。那我们还是沿用这个概念来谈。传输线等长包括差分对内等长,也包括相同类型的传输线组内等长。如果传输线不等长会带来一些信号完整性的问题,包括时序不满足要求、损耗过大或者容易受干扰等等。简单的方式就通过绕线使差分对不同的两段传输线长度一致。

但是在之前的文章中也有给大家介绍过,实际上这种绕线等长,在电学当中它并不能完全满足设计要求。需要适当地调整,使传输线的延时是一致的才好。尤其是对于组内等长(DDR总线),要尤其注意等长设计。

90%的工程师都没意识到的高速电路设计问题:等长绕线的影响

7、跨分割

在PCB设计中,工程师总会在不经意间造成传输线跨分割。对于低速信号可能并不是什么问题,但是对于高速信号而言可能就会引起灾难性的结果。跨分割会引起阻抗不连续、反射、时序以及信号的辐射等等问题。

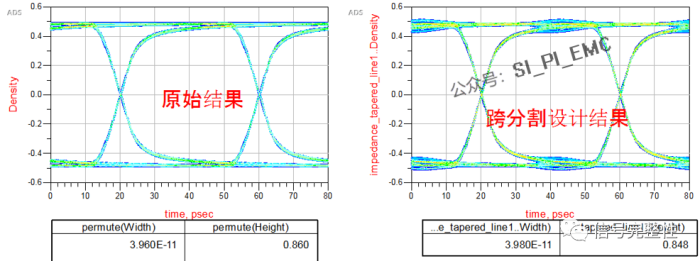

如下是对比跨分割设计与有完整参考平面设计的眼图结果:

显然,跨分割设计的结果会稍微差一些。在PCB设计中,如果不可避免跨分割设计,信号完整性测试设备建议应尽量减少跨分割传输线的长度;尤其是当信号速率比较高(比如25Gbps)时,一旦出现跨分割就要谨慎评估,尽量避免跨分割。

8、拓扑结构

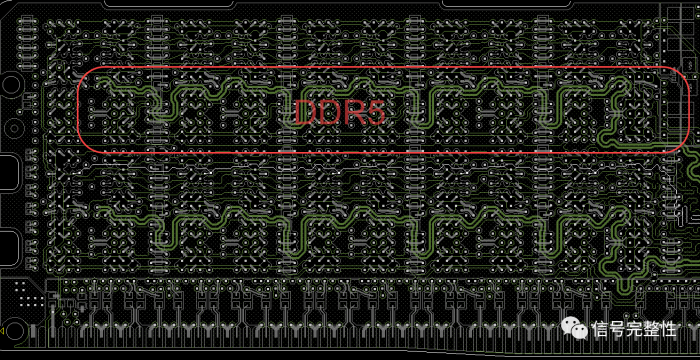

随着电子技术的发展,越来越多的总线都采用点对点的设计,但是有的总线也依然保留着多拓扑结构设计,比如DDR总线,其时钟、地址、控制、命令信号线。如下图所示为DDR5时钟信号的Flyby拓扑结构:

Flyby拓扑结构设计就可能会造成阻抗的不连续,如果要解决这类结构造成的信号完整性问题,就需要做好传输线的阻抗补偿、端接(或者调节ODT)等。

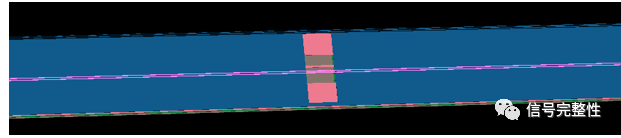

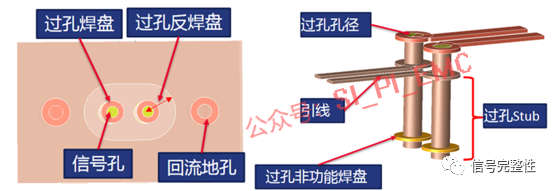

9、过孔

对于多层板的PCB设计,过孔是不可或缺的。对于传输线而言,过孔往往会造成一些阻抗不连续、损耗变大等信号完整性问题。对于高速信号或者高频信号的传输线过孔设计,就需要优化其过孔的结构,比如钻孔的大小、焊盘、anti-pad、Via Stub等等。

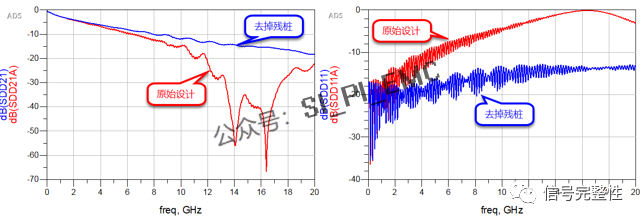

以下是在仿真软件ADS中对比的Via Stub去掉与否的结果对比:

10、电源系统设计

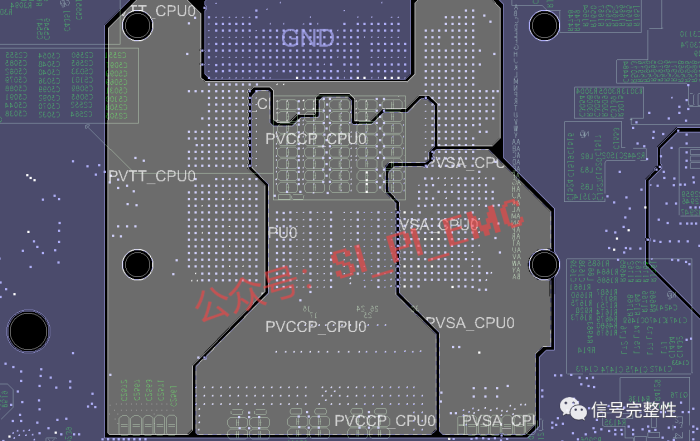

电源系统的设计是电子产品设计的重中之重,电源系统也是容易出问题的地方。在越来越复杂的电子系统中,一个电子系统中可能有10多组电源,或者有的更多,如下是之前设计过的一款服务器CPU处的部分电源平面设计:

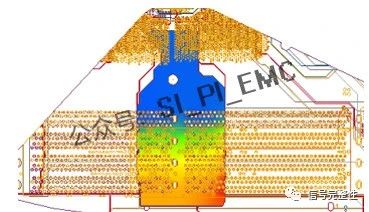

对于做系统产品的工程师而言,如何设计好电源主要分为两个部分,一个是电源系统的电路设计,一个是电源系统的PCB设计。在设计PCB时需要考虑到电源平面的分布和设计以及滤波电容的分布和摆放。为了更合理的设计好这些电源,尽量在设计之初和设计完成之后进行电源完整性的仿真,尽早发现可能存在的问题。如下是一组电源的直流压降仿真结果:

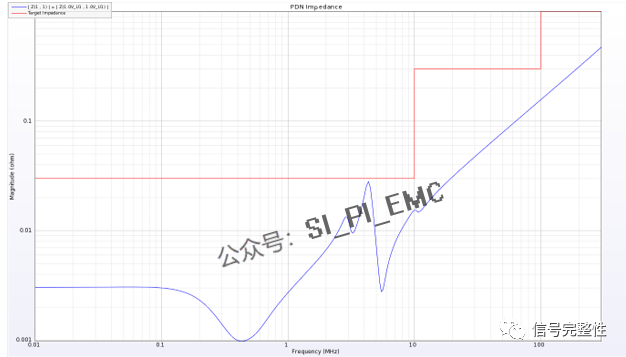

下图是一组电源PDN阻抗分析结果:

11、总结

在越来越复杂、越来越高速、越来越紧凑的电子产品设计中,PCB设计的难度越来越高,信号完整性的问题也越来越多,问题也绝不仅限于本文所介绍的这些。不管任何设计,在设计过程中要有好的设计习惯,设计前和设计后信号完整性测试设备建议尽量使用仿真工具进行仿真分析。