一、MIPI简介

MIPI Alliance即移动产业处理器接口联盟(Mobile Industry Processor Interface 简称MIPI)。于2003 年由ARM,Nokia,ST,TI 等公司成立的为移动应用处理器制定的开放标准和一个规范,目前MIPI已经成为移动领域主流的视频传输接口规范,应用广泛的是MIPI D-PHY和MIPI C-PHY两组协议簇,C-PHY中的许多模块借鉴于D-PHY,两种标准的接口可共用相同引脚实现双模;而MIPI M-PHY和A-PHY,我们后续的文章会有更多分享。

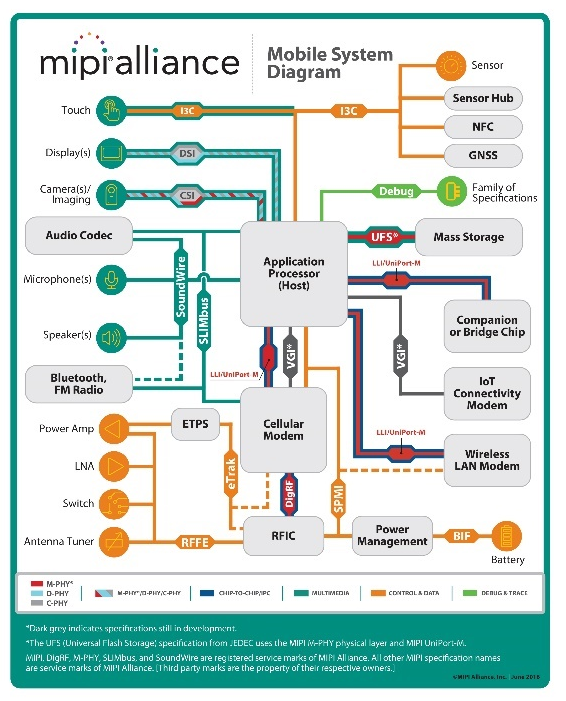

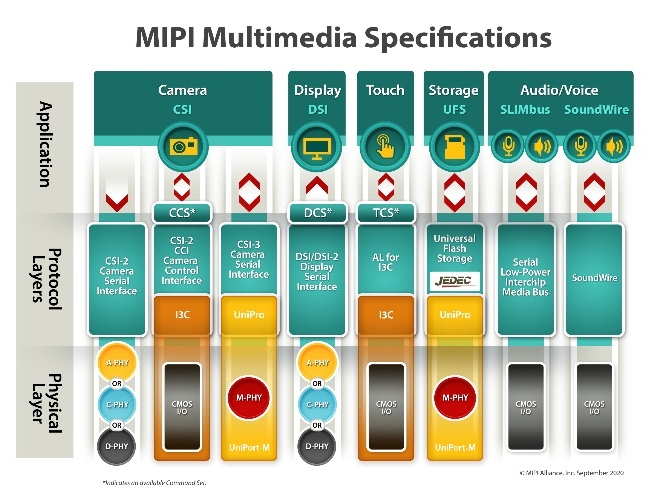

MIPI 联盟下面有不同的 WorkGroup,分别定义了一系列的手机等移动设备内部接口标准,比如摄像头接口 CSI、显示接口 DSI、BBIC与RFIC之间互连的 DigRF、麦克风 /扬声器接口 SLIMbus 等,而MIPI技术是分层的包括物理层、协议层和应用层,相同的PHY物理层可以承载不同协议。如下图是MIPI系统框图和多媒体规范:

图1:MIPI系统框架

图2:MIPI多媒体规范

二、MIPI D-PHY技术概览

MIPI应用为成熟的两个接口如下,其协议层分别是CSI-2、DSI/DSI-2。

(1)摄像头接口:CSI(Camera Serial Interface)

(2)显示接口:DSI(Display Serial Interface)

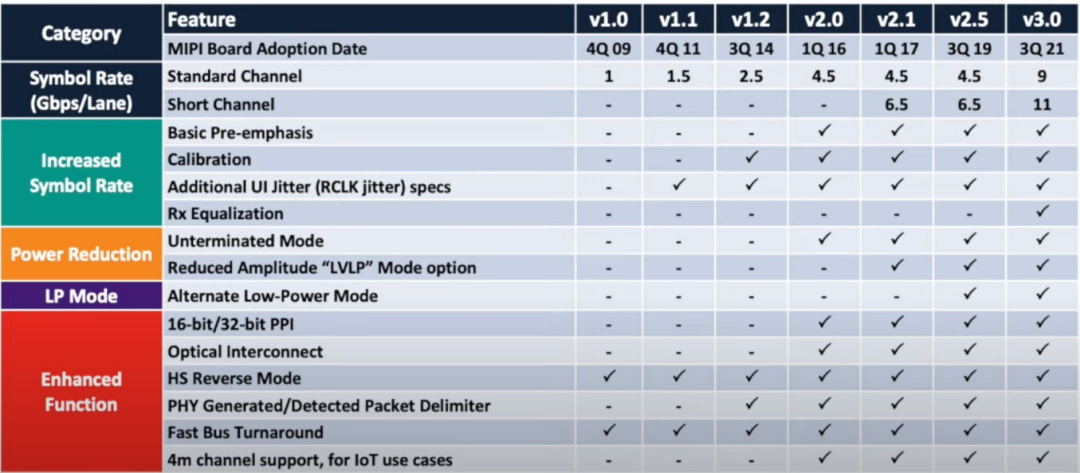

CSI-2、DSI/DSI-2的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前采用的物理层标准是D-PHY和C-PHY,如下是D-PHY的技术演进及各版本技术特点对比。

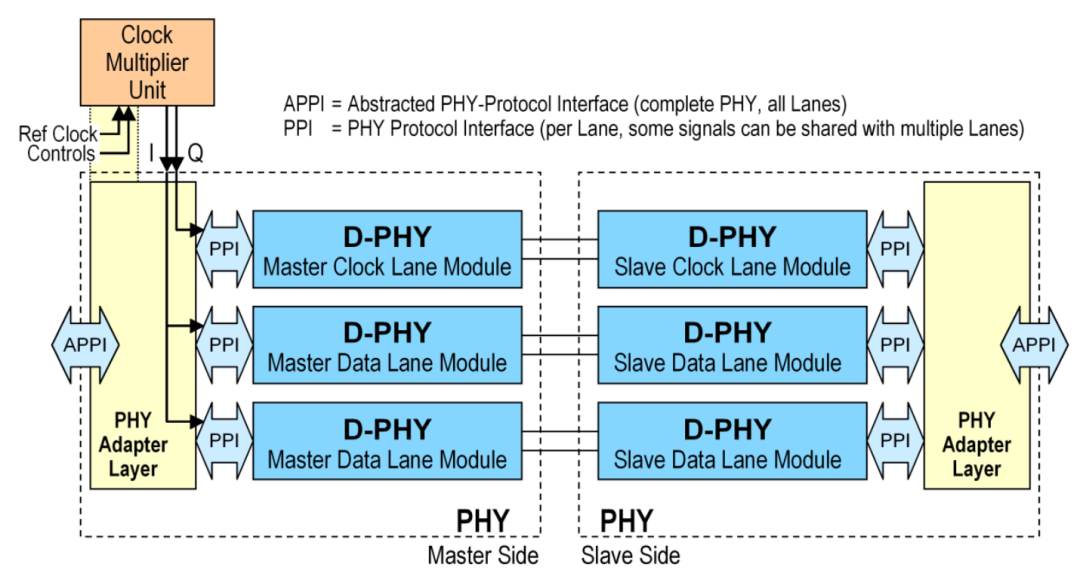

D-PHY实现了Camera/Display(摄像头/显示屏)与AP(应用处理器)之间的互连,具备高速、低功耗、低成本等特点,不仅适合移动应用,也适合IoT。D-PHY提供了主从间源同步接口,包含1对单向差分时钟,支持SSC、1~4对单向或双向差分数据线。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输,下图是D-PHY的Two Data Lane PHY Configuration:

图:D-PHY Two Data Lane PHY Configuration

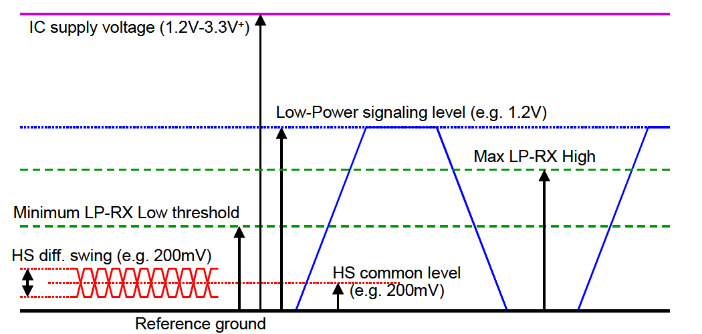

D-PHY 的物理层支持 HS(High Speed)和 LP(Low Power)两种工作模式。HS 模式下采用低压差分信号,有端接,可以传输很高的数据速率(数据速率为 80M~1.5Gbps/without skew cal、1.5G~2.5Gbps/with deskew cal、2.5G~9G/with equalization);LP 模式下采用单端信号,未端接,数据速率很低(<=10Mbps),但是相应的功耗也很低,考虑EMI,产生的信号slew-rate及驱动电流受到限制。可选支持的交替低功耗模式采用有端接的低压差分信号,数据速率低前向4Mbps,反向低1Mbps,高与HS速率保持一致。HS和LP两种模式的结合保证了 MIPI 总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

下图1是HS和LP模式下的信号电平示意图,下图2是用示波器捕获的MIPI D-PHY信号,可以清楚地看到HS和LP信号。

图1:HS和LP模式下的信号电平

图2:示波器捕获的MIPI D-PHY信号

虽然MIPI D-PHY 的板级设计简单,但是MIPI芯片的内部架构、I/O技术非常复杂。复杂体现在如下几个方面:

(1)MIPI通信架构包含发送(通常是master)、接收(通常是slave)及互连通道。

图:MIPI D-PHY 点到点互连

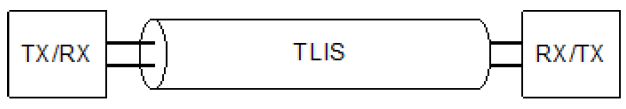

(2)通道类型包括时钟通道、单向数据通道及双向数据通道。收发通道模块包括线路接口、控制/接口逻辑及协议接口。控制/接口逻辑可实现Escape mode encoder这与LP-TX相关、HS-Deskew、Sequences这与HS-TX相关、HS-RX可以实现数据采集、HS-Deskew,LP-RX可实现控制模式下的解码与Escape模式下的解码,LP-CD用于双向数据通道可实现冲突/竞争检测。

电气层面涉及Slew-Rate受控的推挽电路实现的LP-TX,高速低压差分驱动电路实现的HS-TX(可选支持半摆幅模式以实现节电/速率超过2.5Gbps需要2taps的去加重实现2种选择克服ISI影响),高速差分接收电路实现的HS-RX(可使能ZID阻抗),另外LP-RX电路注重低功耗,需要集成迟滞功能降低对噪声的灵敏等。

图:收发内部组成和电气实现

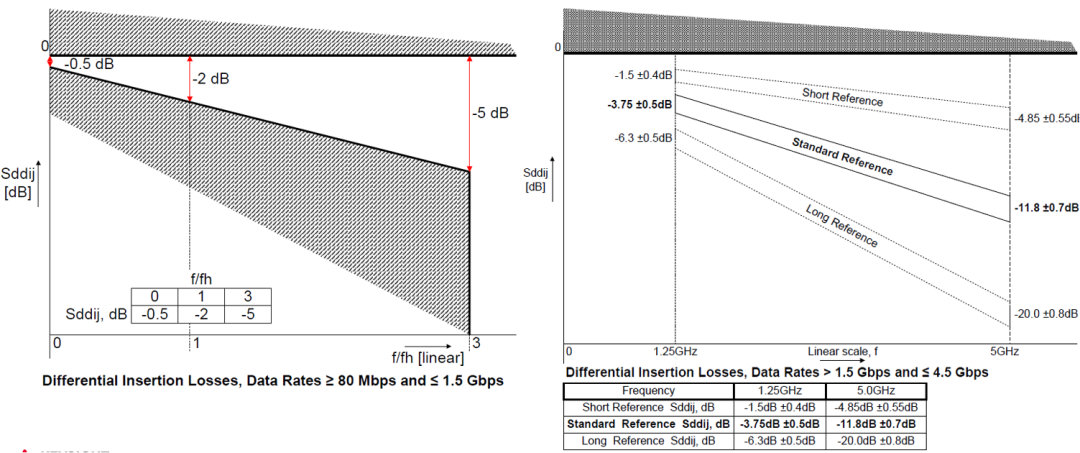

(3)TLIS传输线互连架构支持不同传输“距离”,如下展示了不同速率插损模板,在1.5Gbps~4.5Gbps速率是默认支持Standard Reference channel,Standard Reference channel,可选支持

图:互连插损模板

正是由于复杂内部组成和电气架构,因此要保证接口信号的互通性需要很复杂的测试。MIPI Alliance开发了conformace测试套件(CTS),其目的是优化基于MIPI Spec的产品的互通性。它考察的是物理层功能(不是性能)和compliance test (项目都要通过)有区别,互通性测试通过项目越多,越让开发者自信,以此表明产品可以在许多MIPI的使用环境中正常工作。

以物理层测试为例,发射机测试主要基于示波器,接收机测试基于高速任意波形发生器;而借助自动化的协议分析及解码软件,可以极大的提高debug和测试效率,下面的篇幅,会详细介绍物理层测试。

更多详情请点击:MIPI D-PHY物理层CTS测试及实测难点